摘要:設計了一種基于FPGA的光纖數字接口系統,介紹了運用FPGA實現的HDLC發送功能模塊和接收功能模塊以及CMI編碼解碼模塊,該系統可以有效利用FPGA片內硬件資源,無需外圍電路,高度集成且操作簡單。

關鍵詞:電流縱差保護;FPGA;HDLC;CMI

0. 引言

電流縱差保護廣泛應用于微機繼電保護中,由于需要在輸電線兩端之間傳輸三相電流及時間等數據,其關鍵就是保證傳輸數據的準確性和實時性,不受外界電磁、氣候等影響。隨著電壓等級的提高,白色噪聲、脈沖干擾、電磁場干擾越來越大,極易影響兩端的通訊質量。光纖通訊具有頻帶寬、容量大、傳輸損耗小、中繼距離長、抗強電磁干擾等優點,因此光纖通訊為兩端數據的可靠傳輸提供了保證。

1. 系統設計

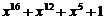

光纖縱差保護裝置的光纖數字接口是裝置中重要組成部分,在進行光纖數字接口設計時,我們沒有采用傳統的芯片堆砌設計方法,而且運用大規模可編程門陣列(FPGA)來實現。在FPGA內部,主要有具有HDLC協議及CRC-16的串行通信控制器(SCC),和光纖線路的編碼解碼(CMI)。光收發器采用RTXM154TL芯片,硬件電路框圖如圖1所示。

圖1 用FPGA實現的光纖數字接口硬件電流框圖

接收過程:光收發器的接收端通過光纖把接收過來的光信號轉換為電信號,此時接收的電信號已經編過碼,經過CMI解碼后送至SCC內部接收FIFO,實現HDLC解碼和串并轉換后,由DSP直接讀走數據。

發送過程:DSP通過數據總線把需要發送的數據寫入SCC的發送FIFO中,SCC根據設定好的HDLC協議,把并行數據轉換為串行幀,發送到CMI,經CMI編碼后送至光收發器,電信號轉換為光信號經過光纖傳至對側。

2. SCC的設計

HDLC協議是高級數據鏈路層協議,是構成SCC的主要部分,在HDLC通信方式中,所有信息都是以幀的形式傳送的,HDLC幀格式如表1所列。

表1 HDLC幀格式示意圖

標志字 | 地址段 | 控制段 | 信息段 | CRC校驗 | 標志字 |

01111110 | 8bit | 8bit | 可變長度 | 16bit | 01111110 |

(1)標志字

HDLC協議規定,所有信息傳輸必須以一個標志字開始,且以同一個標志字結束,這個標志字是01111110(0x7E)。開始標志到結束標志之間構成一個完整的信息單位,稱為一幀。接收方可以通過搜索01111110來探知幀的開始和結束,以此建立幀同步。在幀與幀之間的空載期,可連續發送標志字來做填充。

(2)信息段及“0”比特插入技術

HDLC幀的信息長度是可變的,可傳送標志字以外的任意二進制信息。為了確保標志字是獨一無二的,發送方在發送信息時采用“0”比特插入技術,即發送方在發送除標志字符外的所有信息時(包括校驗位),只要遇到連續的5個“1”就自動插入一個“0”;反之,接收方在接收數據時,只要遇到連續的5個“1”,就自動將其后的“0”刪掉。“0”比特插入和刪除技術也使得HDLC具有良好的傳輸透明性,任何比特代碼都可傳輸。

(3)地址段及控制段

地址字段用于標識接收該幀的地址;控制字段用來表示命令和響應的類別和功能。

(4)CRC校驗

HDLC采用CCITT 標準的16位循環冗余校驗碼(CRC-16)進行差錯控制,其生成多項式為

HDLC差錯校驗指對整個幀的內容作CRC循環冗余校驗, 即對在糾錯范圍內的錯碼進行糾正, 對在校錯范圍內的錯碼進行校驗,但不能糾正。標志位和按透明規則插入的所有“0” 不在校驗的范圍內。

2.1 HDLC發送模塊

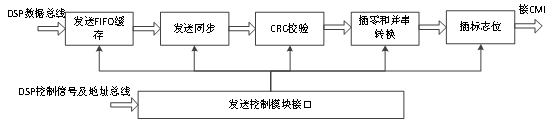

發送模塊主要分為發送控制接口模塊、發送FIFO緩存模塊、發送同步模塊、CRC校驗生成模塊、插零和并串轉換模塊、插標志位模塊。發送模塊示意圖如圖2所示。

圖2 發送功能模塊示意圖

(1)發送FIFO緩存模塊可以存入DSP發送的數據,根據光纖差動要傳輸的數據,緩存大小為256bytes足夠。本設計中,串行發送的速率為了適用于復接設備E1接口,把串行的速率設為2Mbit/s。而DSP讀寫總線數據的速率遠大于2Mbit/s,因此主時鐘和串行收發時鐘的頻率相差較大,而使用FIFO可以有效的協調兩者的頻率差帶來的同步問題。

(2)發送同步模塊負責控制系統時鐘和串行發送時鐘的同步,使相關控制信號完成高低速的匹配。每個進程都是串行時鐘或者系統時鐘的上升沿到來時進行高速和低速或者低速和高速的轉換。

(3)CRC校驗模塊負責生成CCITT標準的CRC-16碼,附加到數據后面。

(4)插零模塊是為了區分幀頭和幀尾的標志位,保證數據鏈路的透明傳輸(即可以傳輸任意組合的比特率),在發送端對傳輸數據進行”0”比特填充。因為幀頭和幀尾為“01111110”,因此當幀連續傳輸了5個“1”比特后,插入一個“0”比特,可避免與標志位相同。

插零和并串轉換的進程:異步置位,時鐘上升沿到來時利用移位寄存器,進行8比特數據的并串轉換,對連續的5比特數據求與運算,5個“1”比特之后,插入一個“0”比特,此時以為寄存器暫停移位。

(5)插標志位主要是對待發送的數據進行幀頭尾的添加。

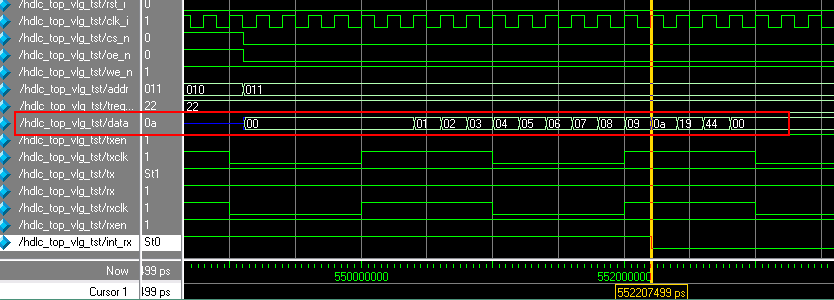

圖3為發送模塊的時序仿真圖。發送的數據為0~10。

圖3 發送模塊時序仿真圖

2.2 HDLC接收模塊

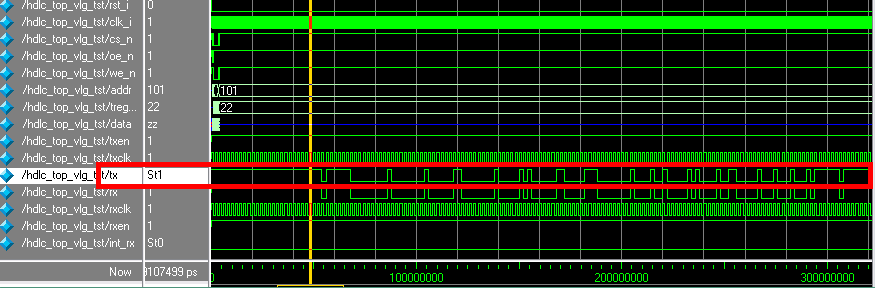

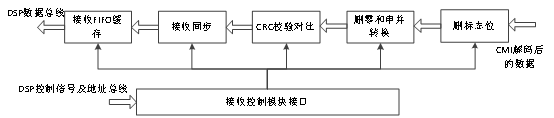

接收模塊主要分為接收控制接口模塊、接收FIFO緩存模塊、接收同步模塊、CRC校驗對比模塊、刪零和串并轉換模塊、刪標志位模塊。接收模塊示意圖如圖4所示。

圖4 接收功能模塊示意圖

(1)刪標志位模塊負責檢測發送的幀頭,確定起始邊界,把CMI解碼后的輸入數據的幀頭和幀尾刪去。

(2)刪零和串并轉換模塊中對比特流中的連續“1”比特進行計數,然后用于刪零判斷、檢測幀結束標志和檢測幀中斷標志的功能。計數器和下一比特在不同值組合下所對應的含義如下:

1 當計數器的值為6,且下一接收比特為“0”,表明檢測到幀結束標志。

2 當計數其的值為5,且下一接收比特為“0”,表明比特“0”應該刪去。

3 當計數器的值為6,且下一接收比特為“1”,表明檢測到中斷標志。

(3)CRC校驗對比模塊把接收到的數據再進行CRC-16計算,其結果與接收到的CRC-16相比較,如果相同,則表示傳輸數據正確,否則舍棄該幀。

(4)接收同步模塊和發送同步模塊一樣,模塊負責控制系統時鐘和串行接收時鐘的同步,使高低速速度轉換。

(5)接收FIFO緩存模塊是把接收的數據存入FIFO緩存,并通知DSP可讀取數據,DSP發生外部中斷后把數據讀走。

圖5為接收模塊的時序仿真圖。接收的數據為0~10。

圖5 接收模塊時序仿真圖

3. CMI編碼和解碼設計

光纖線路中線路碼型傳輸性能的好壞直接影響光系統的傳輸性能。傳輸性能好的線路碼型應該符合比特序列獨立性好、功率譜密度中的高低頻成分少、定時成分多、直流電平比較恒定、誤碼擴展系數小、碼結構均勻等特征。適于光線路傳輸的碼型比較多,本設計采用CMI碼型。其變換模式為:“0”碼變換為“01”,“1”碼變換為交替的“00”和“11”碼。

4. 結束語

與傳統的芯片電路相比,采用大規模可編程門陣列(FPGA)芯片具有以下一些優點:

(1)通信板結構簡單,便于硬件設計,只需一塊FPGA芯片可完成以上設計,占用PCB板空間小。

(2)可實現各功能模塊之間的無縫連接。由于各功能模塊的邏輯均在一個芯片內部完成,不存在相互之間電平匹配問題。

(3)時序控制簡單。在芯片內部只需進行同意的時序控制即可,不需要考慮對不同的芯片進行不同的時序控制。

(4)可靠性高。采用FPGA芯片消除了由于不同芯片廠家生產的芯片的參數不同而造成通信不穩定現象,提高了通信的穩定性能。

本文采用了FPGA實現的SCC和CMI功能,調試結果表明,該系統操作簡單、使用靈活、能夠很好地應用于電力系統繼電保護光纖通訊系統中。

參考文獻:

[1]. 唐成虹等. 光纖縱差保護裝置中光纖數字接口的設計新方法.電力系統自動化.2005

[2]. 婁景藝等. HDLC控制協議的FPGA設計與實現.國外電子元器件.2005